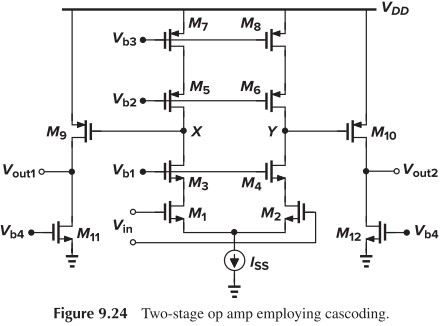

9.8 Suppose the circuit of Fig. 9.24 is designed with $I_{SS}$ equal to 1 mA, $I_{D9}–I_{D12}$ equal to 0.5 mA, and $(W/L)_{9−12} = 100/0.5$.

- (a) What CM level is required at $X$ and $Y$?

- (b) If $I_{SS}$ requires a minimum voltage of 400 mV, choose the minimum dimensions of $M_1–M_8$ to allow a peak-to-peak swing of 200 mV at $X$ and at $Y$.

- (c) Calculate the overall voltage gain.

Solution:

(a) X and Y are symmetrical.

\[\vert V_X-V_{DD} \vert - \vert V_\tx{THP} \vert = \sqrt{\frac{2I_{D9}}{\mu_p C_\tx{ox} (W/L)_9}} = 0.289 \tx{V}\\ \Rightarrow V_{X,\tx{CM}} = V_{Y,\tx{CM}} = 1.911 \tx{V}\](b) The maximum of $V_X$ is $V_{X,\tx{CM}}+100\tx{mV}$, which is limited by $M_5,M_7$, i.e.

\[V_{X,\max} = V_{DD}-V_{OD7}-V_{OD5}\]if $V_{OD5}=V_{OD7}$, we have

\[V_{OD5}=V_{OD7}=\frac{V_{DD}-V_{X,\tx{max}}}{2}=0.495 \tx{V}\] \[\left( \frac{W}{L} \right)_5 = \frac{2I_D}{\mu_P C_\tx{ox} V_{OD5} (1+\lambda V_{DS})}=97.02\\ W_5 = 97.02 \times L_\tx{eff} = 31.05 {\rm \mu m}\]The minimum of $V_X$ is $V_{X,\tx{CM}}-100\tx{mV}$, which is limited by $M_1,M_3$, i.e.

\[V_{X,\min} = V_{ISS}+V_{OD1}+V_{OD3}\]if $V_{OD1}=V_{OD3}$, we have

\[V_{OD1}=V_{OD3}=\frac{V_{X,\min}-V_{ISS}}{2}=0.7055 \tx{V}\] \[\left( \frac{W}{L} \right)_1 = \frac{2I_D}{\mu_P C_\tx{ox} V_{OD1} (1+\lambda V_{DS})}=14\\ W_5 = 14 \times L_\tx{eff} = 4.8 {\rm \mu m}\](c) $A_v = g_{m1}(g_{m3}r_{O3}r_{O1}\Vert g_{m5} r_{O5} r_{O7} ) g_{m9}(r_{O9}\Vert r_{O11})$

\[\begin{aligned} g_{m1} &= g_{m3} =\frac{2I_D}{V_{GS1}-V_\tx{TH}}=1.417 \tx{mG}\\ g_{m5} &= \frac{2I_{D}}{V_{GS5}-V_\tx{TH}} = 2.022 \tx{mG}\\ g_{m9} &= \frac{2I_{D}}{V_{GS9}-V_\tx{TH}} = 3.46 \tx{mG}\\ r_{ON} &= \frac{1}{\lambda I_D} = 20 {\rm k\Omega}\\ r_{OP} &= \frac{1}{\lambda I_D} = 10 {\rm k\Omega} \end{aligned}\]代入原式得:

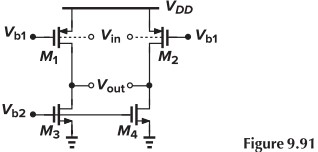

\[A_v = 4871\]9.22 It is possible to use the bulk terminal of PMOS devices as an input. Consider the amplifier shown in Fig. 9.91 as an example.

- (a) Calculate the voltage gain.

- (b) What is the acceptable input common-mode range?

- (c) How does the small-signal gain vary with the input common-mode level?

- (d) Calculate the input-referred thermal noise voltage and compare the result with that of a regular PMOS differential pair having NMOS current-source loads.

Solution:

(a) the drain current is given by $g_{mb}V_\tx{in}$. Thus, $A_v = -g_{mb} (r_{O1} \Vert r_{O3})$

(b) the bulk and source diode must be inverse bias. Thus, $V_\tx{in}>V_{DD}-V_\tx{diode,TH}$

(c) $g_{mb}=g_m \dfrac{\gamma}{2\sqrt{\vert 2 \phi_F \vert+\vert V_{SB} \vert}}$. As $V_\tx{in,CM}$ increases, $\vert V_{SB} \vert$ decreases, $g_{mb} \downarrow\Rightarrow A_v \downarrow$

(d) 输出噪声电压和一般的差动放大器是一样的,但由于增益不同,输入噪声电压不同。

\[\begin{aligned} \overline{V_{n,\tx{out}}^2} &= [4kT \gamma (g_{m1}+g_{m3})R_\tx{out}^2]\times 2\\ \overline{V_{n,\tx{in}}^2} &= \frac{\overline{V_{n,\tx{out}}^2}}{A_v^2}\\ &= \left[ 4kT\gamma \frac{g_{m1}+g_{m3}}{g_{mb1,2}^2}\right] \times 2 \end{aligned}\]