概览

Use Ctrl+F to search particular abbreviation.

- EDA - Electronic Design Automation 电子设计自动化

- SOC - System on Chip 系统级芯片

- ASIC - Application Specific IC 专用集成电路

- HLS - High Level Sythesis 高级综合

- PAL - Programmable Array Logic 可编程阵列逻辑

- GAL - Generic Array Logic 通用阵列逻辑

- PLD - Promgrammable Logic Device 可编程逻辑器件

- CPLD - Complex PLD 复杂可编程逻辑器件

- FPGA - Field Programmable Gate Array 可编程门阵列

- HDL - Hardware Description Language 硬件描述语言

- VHDL - Very high speed ic HDL VHSIC硬件描述语言

- LMC - Logic Macro Cell 可编程逻辑宏单元

- OLMC - Output LMC 输出逻辑宏单元

- CLB - Configurable Logic Block 可配置逻辑块

- IOB - I/O Block 可编程输入输出单元

- LAB - Logic Array Block 逻辑阵列块

- PLL - Phase Locked Loop 锁相环

解释

PLD 是可通过编程实现不同逻辑功能的器件。我们可以利用 EDA 工具来编程,编程完后有一定功能的器件称为 ASIC.

PLD 器件按照复杂度分为

- SPLD(Simple PLD)

- PROM

- PLA

- PAL

- GAL

- HCPLD(High Capacity PLD)

- CPLD

- FPGA

各种 PLD 的特点如下:

| Product | Features | 原理 |

|---|---|---|

| PROM(Programmable Read-Only Memory) | Fuse Program | OR programmable |

| PLA(Programmable Logic Array) | Fuse Program | And/OR programmable |

| PAL(Programmable Array Logic) | CMOS technology | AND programmable |

| GAL(Generic Array Logic) | Multi-times Programming | AND programmable |

| FPGA | LUT technology | Look-up Table |

| EPLD | Erasable | |

| CPLD | ISP technology | Product-term |

PROM

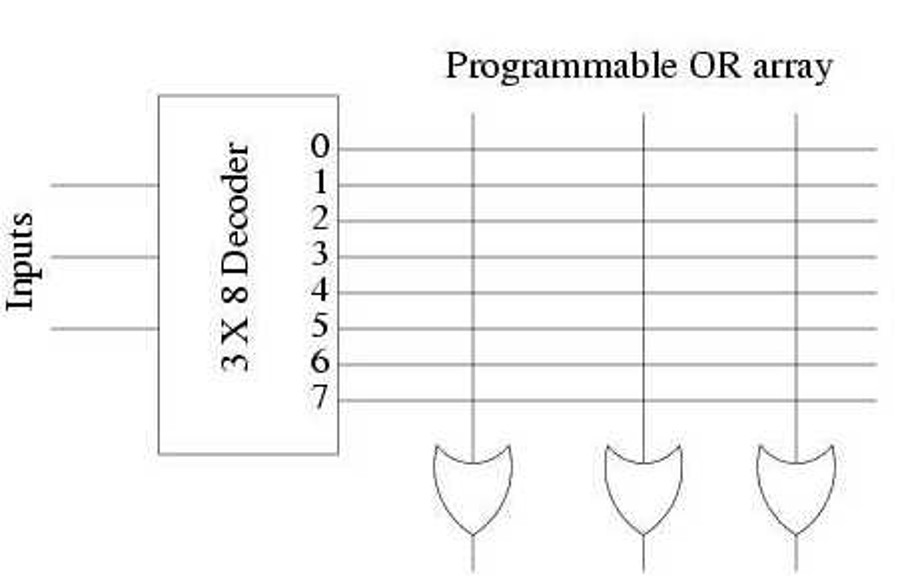

PROM 的原理见下图,本质上就是数电中的和式,只能改变或门的输入。设输入是 $N$ bits,输出是 $M$ bits,那么 ROM 一共有 $2^N \cdot M$ bits

PLA

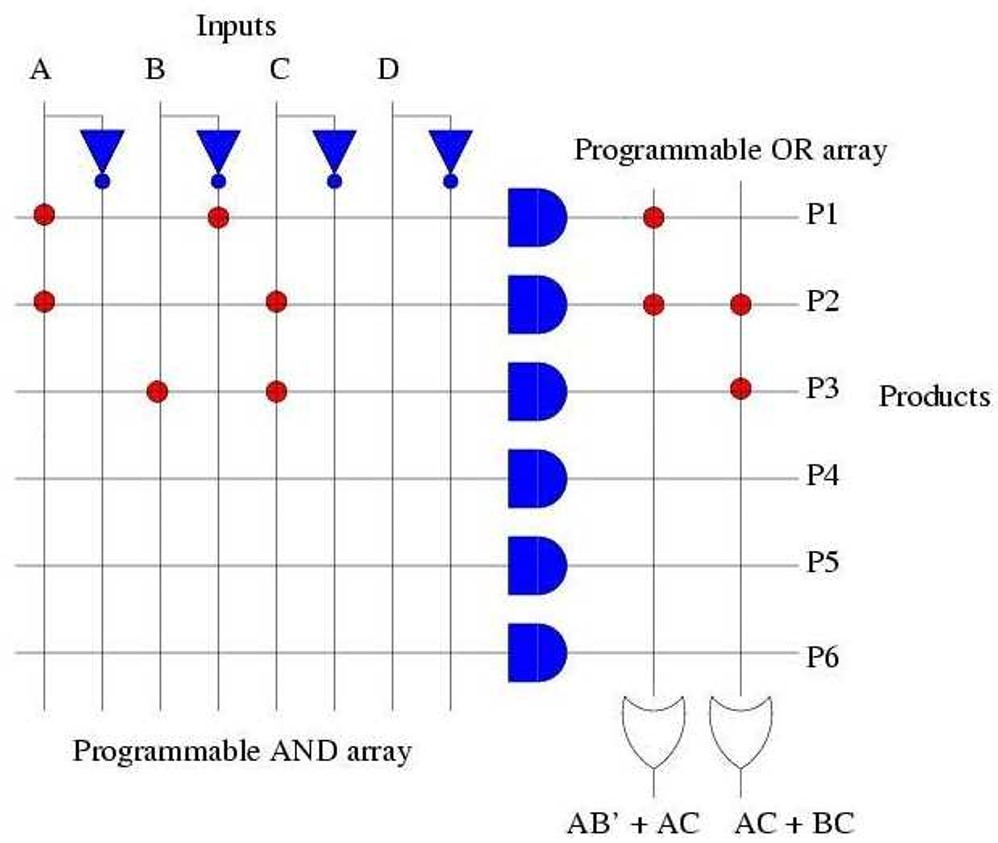

PROM 中通过 Decoder 列出了输入所有可能的组合,有时候只需要某些输入组合,所以就要 PLA。显然 PLA 能表示的逻辑组合不多余 PROM,但它的结构比较简单。

PAL

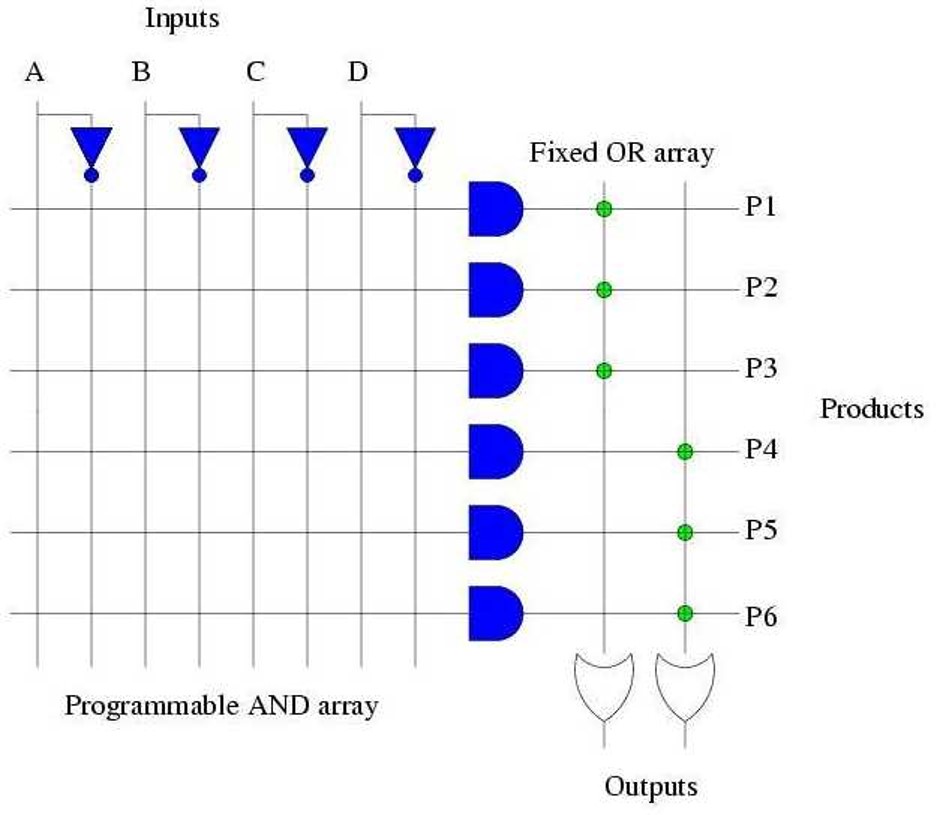

PAL 就是将 PLA 中的或门固定,只能改变与门。

CPLA

CPLA 就是将多个 PAL-like Block 集成到一起来实现更复杂的功能

FPGA

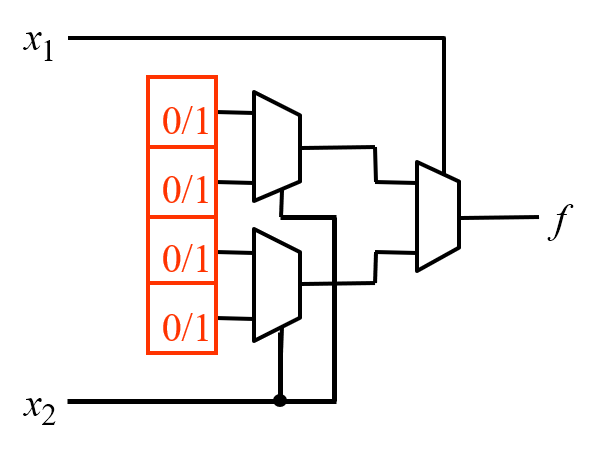

与上面用与或门的实现方式不同,FPGA 使用 LUT(Look-up table)作为器件单元。一个简单的 LUT 示例如下,它有三个 MUX(选择器),外部输入作为选择端,我们通过配置选择器的输入来实现不同逻辑功能。

选择器的输入存储在 storage cell 中,有 $N$ 个外部输入,就要有 $2^N$ 个存储器。