3.1 Introduction to Device Fabrication

半导体公司可以分成三类:

- integrated semiconductor companies: both design and fabricate ICs

- fabless: only design the circuits

- foundries: specialize in manufacturing

根据 IC 的规模,可以分成:

- LSI (large-scale integration, 104 transistors on a chip)

- VLSI (very large-scale integration, 106 transistors on a chip)

- ULSI (ultra-large-scale integration)

- GSI (giga-scale integration).

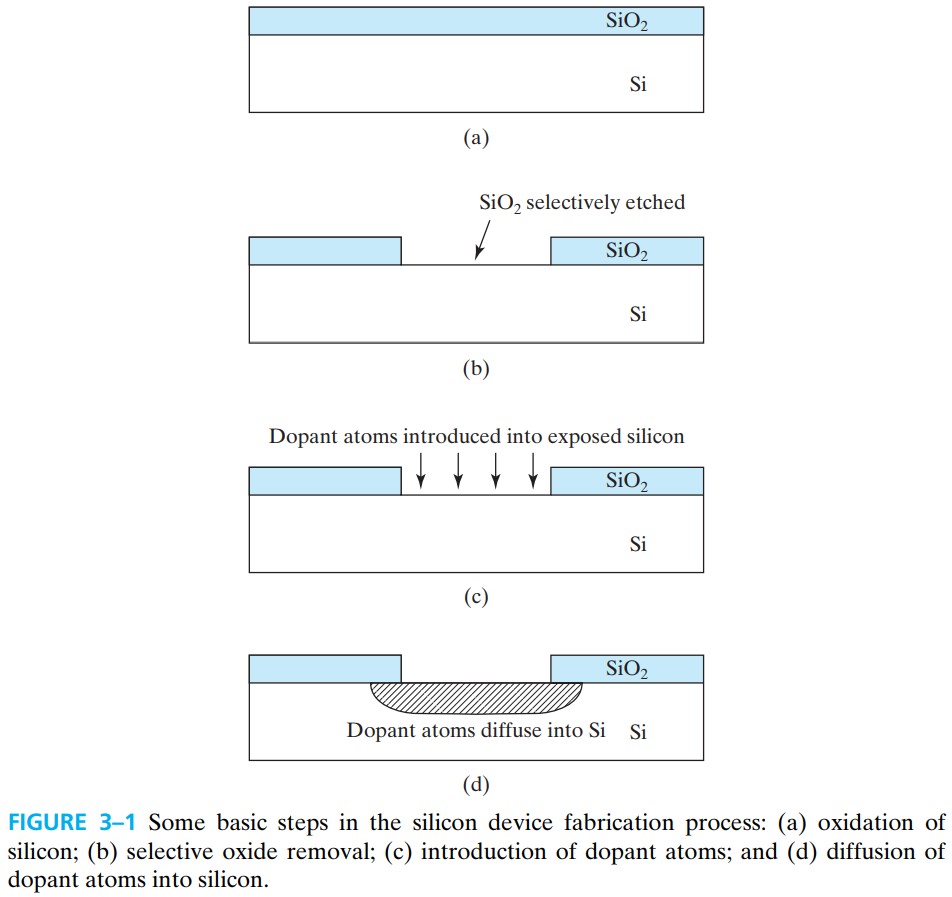

一个简单的制造过程如下:整个过程是在一片 wafer (晶圆)上制造的,先构造 ${\rm SiO_2}$ 层,然后选择性的去除某些部分,然后在这部分的表面引入杂质离子,最后使杂质离子扩散进硅。

这种一层一层将电路做在 wafer 上的技术叫 planar technology

3.2 Oxidation of silicon

silicon dioxide 有两种用途:

- serving as a mask against dopant introduction into silicon

- serving as the most critical component in the metal-oxide-semiconductor transistor

有两种方式制造 ${\rm SiO_2}$ layer,对应两种化学反应:

- dry oxidation:${\rm Si+O_2 \rightarrow SiO_2}$,slow and thin

- wet oxidation:${\rm Si+2H_2O \rightarrow SiO_2+2H_2}$,fast and thick

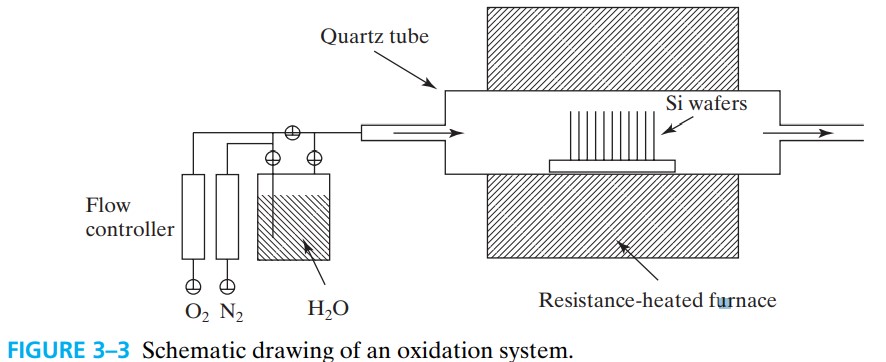

步骤如下:

- wafer loading:Si wafer 先放在 quartz boat 上

- insertion into the furnace:推到 furnace 中进行反应

- ramping of the furnace temperature:furnace 的反应区一般是用 clear fused quartz 或 SiC 或 polycrystalline Si 制造的,通过 electrical resistance heating coils 加热到 700–1,200 °C

- gas control:通入氧气或用carrier gas带出水汽来进行反应,

- 整个过程是自动化控制的。

可以通过控制氧化温度和时间来控制厚度。另外, the ambient gas 和 the Si surface orientation 也会影响厚度(这也是为什么要沿 (100) plane 切)。

3.3 Lithography

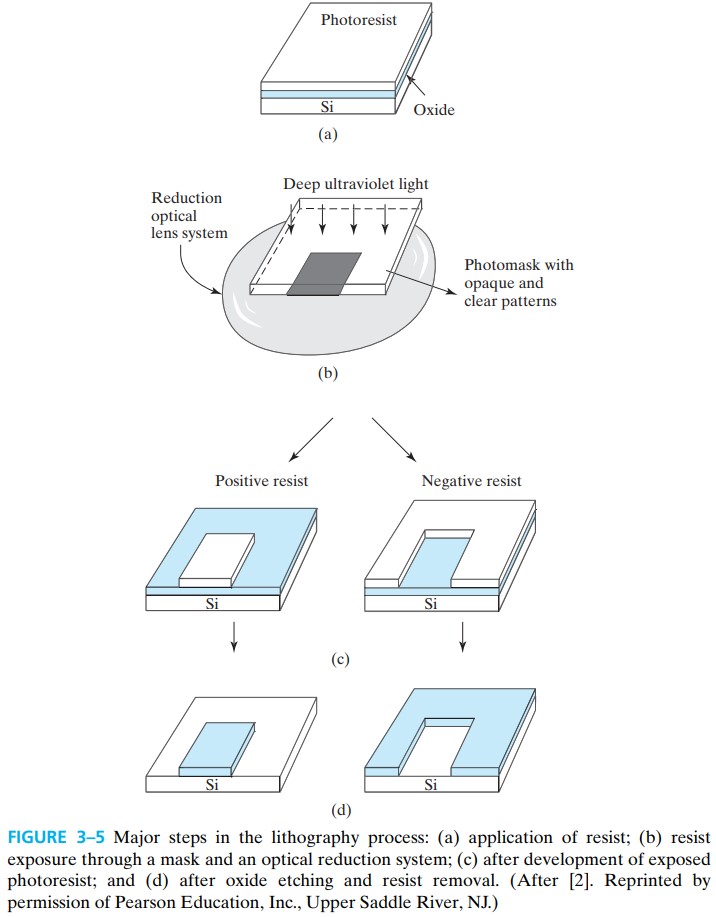

要选择性去除氧化层,要通过光刻,光刻分为两步:图形曝光(photolithography or optical lithography 以及刻蚀(etching. 步骤如下(1~4为图形曝光,5~6为刻蚀):

- 覆盖光刻胶(也叫抗蚀剂 photoresist,an ultraviolet (UV) light sensitive material):Liquid photoresist is placed on the wafer, and the wafer is spun at high speed to produce a thin, uniform coating.

- 前烘: a short bake at about 90 °C is performed to drive solvent out of the resist.

- 曝光:expose the resist through a photomask and a high-precision reduction lens system using UV ligh

- The photomask (掩模版) is a quartz photoplate containing the patterns to be produced

- negative resists (负胶,曝光不溶):the areas where the light strikes become polymerized and more difficult to dissolve in solvents

- Positive resists (正胶,曝光溶):contain a stabilizer that slows down the dissolution rate of the resist in a developer. This stabilizer breaks down when exposed to light, leading to the preferential removal of the exposed regions.

- 显影:用显影剂溶解未固化的光刻胶,然后将硅片冲洗和甩干

- 去除氧化层:Buffered hydrofluoric acid (HF) may be used to dissolve unprotected regions of the oxide film

- 去除光刻胶 (resist strip):This is accomplished by using a chemical solution or by oxidizing or “burning” the resist in an oxygen plasma or a UV ozone system called an asher.

曝光的分辨率受光波长和光学衍射限制,可以用下面公式表示:

\[\text{Lithography Resolution}=k\lambda\]- 减小光波长:难, lack of suitable transparent materials for lenses and mask plates

- 减小 k 值:

- 减小曝光范围(lithography field ),用 stepper 移动 wafer 直到全部曝光

- 优化 photomask,用 optical proximity correction (OPC) 修正,避免相邻线之间相互影响

- 使用 phase-shift photomask:产生两束靠得很近的光,两光相位相反,在中间产生的衍射恰好相互抵消

下面介绍多种曝光方法。

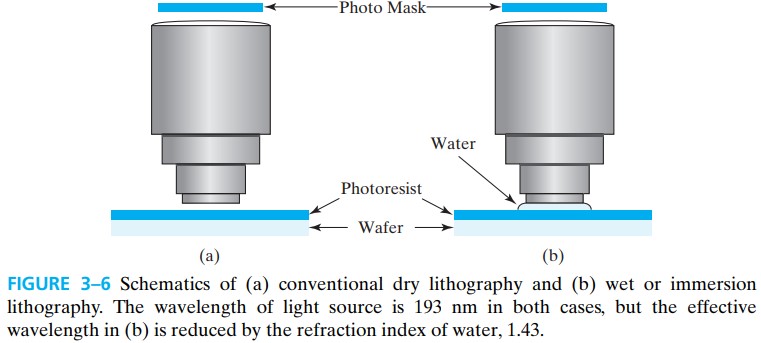

3.3.1 Wet Lithography

wet lithography or immersion lithography 简单来说就是在 lens 和 photoresist 中间放水,因为有折射,所以波长会减小:

\[\frac{n_1}{n_2}=\frac{\lambda_2}{\lambda_1}\]

3.3.2 Electron Lithography

electron-beam lithography 就是直接用电子束将光刻胶去除,因为电子束的波长远小于光,所以分辨率更高。不过由于电子束需要逐点扫描(不用掩模版),效率很低,一般用来验证设计。

3.3.3 Nanoimprint

Nanoimprint 不需要曝光,直接像盖章一样将 patterns 压在一层 soft coating 上,然后经过 coating hardens 得到图形。

3.4 Etching

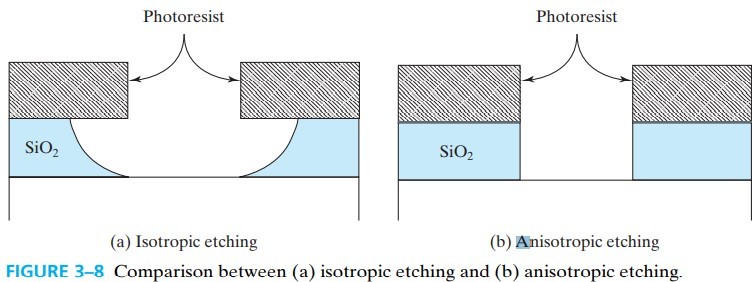

刻蚀就是将曝光得到的 photoresist 上的pattern 转移到下一层(${\rm SiO_2}$)。有两种刻蚀方法:

- wet etching:${\rm SiO_2}$ is removed with ${\rm HF}$

- 特点:isotropic(各向同性)material selectivity好

- dry etching:also known as plasma etching or reactive-ion etching or RIE,用等离子去轰击

- 特点: anisotropic(各向异性的)material selectivity差,有可能造成某些破坏(antenna effect)

3.5 Doping

掺杂分成两步:

- 在表面放上杂质原子

- ion implantation

- gas-source doping

- solid-source diffusion

- 扩散进内部 drive-in diffusion

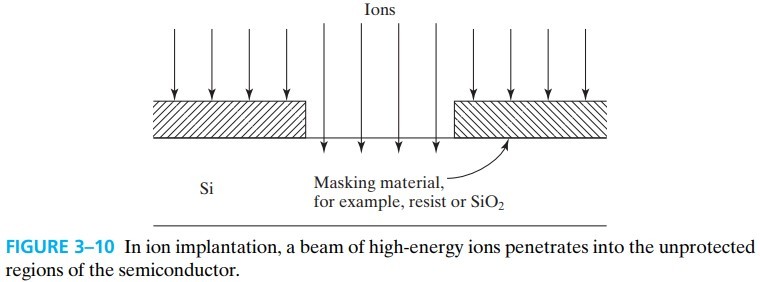

3.5.1 Ion Implantation

就是将 ions 加速到很高能量,然后射到表面。会对晶体造成破坏,所以需要通过 anneal for damage removal and for dopant activation

3.5.2 Gas-Source Doping

只适用于掺 phosphorus(磷),因为只有磷有合适的气体。这个过程类似于 3.2 的wet oxidation,只不过将水换成了 ${\rm POCl_3}$,发生的反应如下:

\[{\rm 5 POCl_3 \xrightarrow{>600 ℃} 3PCl_5+P_2O_5}\\ {\rm 2P_2O_5 + 5Si \rightarrow 5 SiO_2 + 4P\downarrow}\]3.5.3 Solid-Source Diffusion

先在硅表面弄一层包含 dopant 的薄层,然后等到 dopants 扩散进去后移除薄层

3.6 Dopant Diffusion

The dopant impurity diffuses with time at high temperature. 将相反的杂质掺进去可以得到 PN junctino,它的 junction depth 指的是从表面到 $N_a=N_d$ 的厚度。杂质原子的浓度与深度的关系满足高斯分布:

\[N(x,t)=\frac{N_0}{\sqrt{\pi D t}} e^{-x^2/4Dt}\]- $N_0$ is the number of dopants per square centimeter and is determined by the dopant addition step

- $x$ is the distance into the semiconductor

- $D$ is the diffusivity for the given impurity and furnace temperature

- $t$ is the time for the diffusion step

3.7 Thin-Film Deposition

除了掺杂外,我们还需要再硅表面做各种膜(氮化硅、二氧化硅、各种金属),有下面几种方法

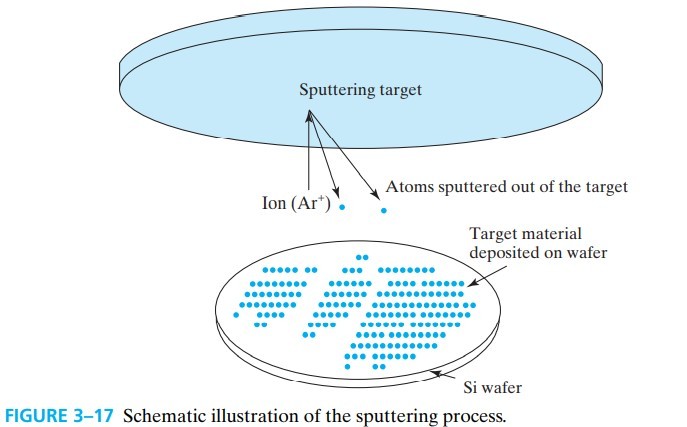

3.7.1 Sputtering

- Sputtering is performed in a vacuum chamber

- sputtering target(提供原子源的材料)和 wafer 形成一对平行面板

- 抽真空后,充入 sputtering gas (typically Ar)

- 先让 Ar 电离,形成等离子体,然后加交变电场,让 Ar 轰击 sputtering target

- 轰击下来的 target atoms 沉积在 wafer 上

整个过程主要是用物理方法,所以也叫 physical vapor deposition (PVD)

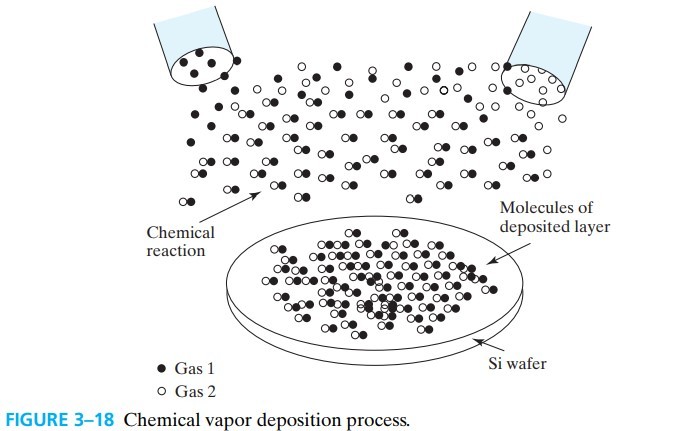

3.7.2 Chemical Vapor Deposition (CVD)

PVD 不能覆盖垂直的地方,所以需要 CVD to deposits a much more conformal film. 大概过程就是两种气体反应形成固体,然后沉积在 wafer 上

常用的 CVD 包括:

- high-temperature oxide (HTO)

- lowpressure chemical vapor deposition (LPCVD)

- plasma-enhanced chemical vapor deposition (PECVD)

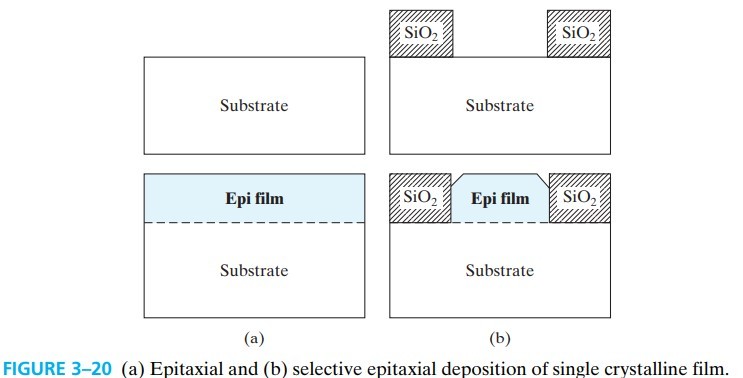

3.7.3 Epitaxy

Epitaxy(磊晶;外延)用于在晶体上长晶体。方法于 CVD 类似, at sufficiently high temperature, an arriving atom can move over the surface till it stops at a correct location to perfectly extend the lattice pattern of the substrate crystal.

3.8 Interconnect - The Back-End Process

将器件用金属线连接的过程称为 metallization,过程如下:

- 移除二氧化硅

- PVD 形成金属膜

- 通过刻蚀移除多余的金属

一开始用的是 Aluminum,但 Al 存在 electromigration(原子随电流迁移),所以现在都是用 Cupper。